# **ACCELERATING THE DATA-CENTRIC WORLD**

DEVICES / EDGE

**NETWORK**

CLOUD/DATA CENTER

REMOVING DATA BOTTLENECKS WITH FPGA ACCELERATION

# IA+ FPGA: ACCELERATING BUSINESS OUTCOMES

LOWER LATENCY

HIGHER PERFORMANCE

MULTI-FUNCTIONAL

• HIGH THROUGHPUT I/O

1000s OF PARALLEL PROCESSING UNITS

**PROGRAMMABLE**

BUSINESS OUTCOMES Real-time actionable intelligence at the edge New revenue streams for Communication service providers Improved total cost of ownership (TCO) in the cloud

# INTEL SCALE DRIVING VALUE AND GROWTH

# YEAR-OVER-YEAR REVENUE GROWTH

| ]///in [[                                  | 1H '18 |

|--------------------------------------------|--------|

| DATA CENTER                                | 140%   |

| ADVANCED<br>PRODUCTS (28NM,<br>20NM, 14NM) | 50%    |

| TOTAL REVENUE                              | 17%    |

\*Revenue excludes Intel products with integrated FPGAs

## BETTER TOGETHER: SOLUTIONS ACROSS MARKETS

IA+FPGA SOLUTIONS

**IP & ECOSYSTEM**

INTEL PARTNERSHIPS: IP, OEM, SI, ISV, VAR

**SOFTWARE**

INTEL+FPGA FLOWS: SOFTWARE-CENTRIC DESIGN METHODOLOGY

SILICON/BOARDS

HW LEADERSHIP: SILICON, BOARDS, FPGA ACCELERATION CARDS

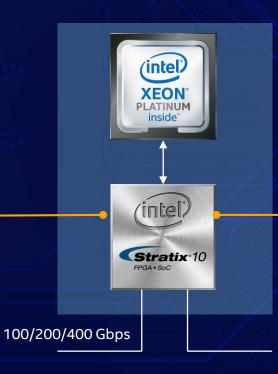

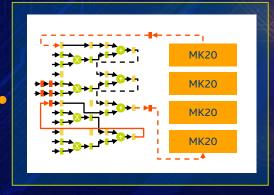

## MULTI-FUNCTION ACCELERATION IN THE DATA CENTER

## **INFRASTRUCTURE ACCELERATION**

NETWORK | STORAGE | SECURITY

Intel® Xeon® processor cores

Applications Infrastructure

### **LOOK-ASIDE ACCELERATION**

AI INFERENCE VIDEO TRANSCODE APPLICATIONS (DATABASE) SEARCH

## FPGA: BECOMING MAINSTREAM IN ENTERPRISE

Dell R640, R740, R740xd

- **→** A

- FINANCIAL

- VIDEO PROCESSING

- **CYBERSECURITY**

- **GENOMICS**

### **GROWING LIST OF SOLUTION ACCELERATION PARTNERS**

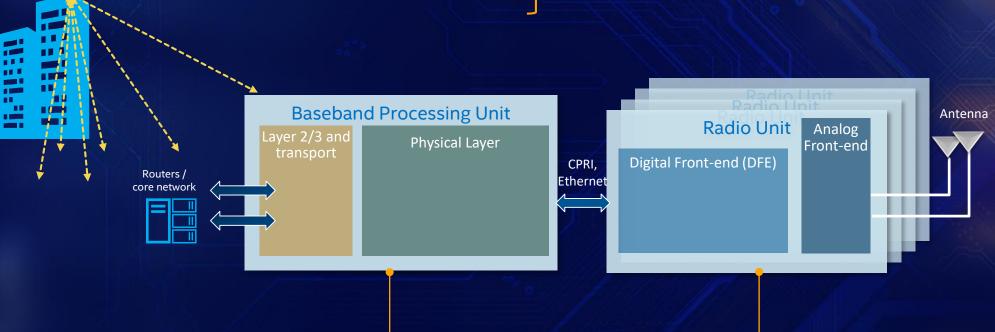

## END-TO-END SOLUTIONS FOR 5G

1000X CAPACITY INCREASE

5X DECREASE IN LATENCY

EVOLVING 3GPP STANDARDS

- 5G NETWORK CHALLENGES

**1M+ BASEBAND UNITS IN 2022**

**5M+ RADIO UNITS IN 2022**

## END-TO-END SOLUTIONS FOR NFV

**NFV**

### **NETWORK INFRASTRUCTURE**

**Physical Appliances**

Single application on dedicated hardware and proprietary management

ASIC, DSP, FPGA, ASSP

### FLEXIBLE CLOUD INFRASTRUCTURE

Industry-Standard x86 Servers

Decoupled software on standard x86 server hardware solution agnostic management

**MANAGEMENT & ORCHESTRATION**

**H/W Accelerators**

Compute

Storage

Networking

**FPGA**

## ACCELERATION AT THE EDGE

## **PERFORMANCE AND POWER**

High-capacity memory High -peed I/O RAID & 10Gbe

Video playback Transcoding VMS, Video **Analytics & Sensor** aggregation

Excellent image quality Image enhancement **Encoding & Analytics**

inside~

## **EDGE WORKLOADS**

**SURVEILLANCE**

**SMART RETAIL**

**INDUSTRY 4.0**

**SMART CLASSROOM**

# **ACCELERATING AI WITH FPGA**

## **SI ADVANTAGES**

**SUPPORT EVOLVING AI TOPOLOGIES**

HIGH ON-CHIP MEMORY FOR INCREASED THROUGHPUT

**LOW LATENCY INFERENCE**

**ENERGY-EFFICIENT INFERENCE**

## TOOLKITS

Application Developers

#### OpenVINO™ †

<u>O</u>pen <u>V</u>isual <u>I</u>nference & <u>N</u>eural Network <u>O</u>ptimization toolkit for inference deployment on CPU/GPU/FPGA for TensorFlow\*, Caffe\* & MXNet\*

### **FOUNDATION**

Library Developers

#### Intel® nGraph™ Compiler

Open-sourced compiler for deep learning model computations optimized for multiple devices from multiple frameworks

## **ACCELERATION OF AI FOR EARTH**

WITH MICROSOFT'S AI FOR EARTH PROGRAM WE ARE PUTTING OUR CLOUD AND AI TOOLS IN THE HANDS OF THOSE WORKING TO SOLVE GLOBAL ENVIRONMENTAL CHALLENGES - A TOPIC THAT REQUIRES COMBINING BIG DATA, BIG COMPUTE, AND EFFICIENT ALGORITHMS. DEPLOYING DEEP NEURAL NETWORK MODELS TO FIELD-PROGRAMMABLE GATE ARRAY (FPGA) SERVICES USING MICROSOFT PROJECT BRAINWAVE IS ONE SUPER SIMPLE WAY TO ACHIEVE THIS. RECENTLY WE USED THIS FPGA SERVICE TO PERFORM LAND COVER MAPPING OF THE ENTIRE UNITED STATES, ANALYZING 10 TRILLION PIXELS ACROSS 20 TB OF AERIAL IMAGERY. MICROSOFT PROJECT BRAINW **USING INTEL FPGAS, SCORED THESE 200 MILLION IMAGES IN ENTIRETY IN JUST OVER 1** MINUTES FOR A COST OF \$42.

Doug Burger

Technical Fellow, Azure HW Systems Group

# EASIC ACQUISITION DRIVING MARKET EXPANSION

#### **FPGA**

Programmable Input & **Output Blocks**

can be programmed to do many types of I/O

**Programmable Logic Blocks**

can be programmed to do many functions

1/2 THE COST 1/2 THE POWER

**Massive Amounts** of Programmable Routing can be programmed to connect from anywhere to anywhere

**Structured ASIC**

**Fixed Function Input** & Output Blocks single function

**Fixed Function** Logic Blocks

single function

**Fixed Routing** point to point interconnect

- Cost and power reduction path for **FPGA** customers

- Lower NRE cost and time-to-market for **ASIC** customers

- Scalable technology to provide pathway to cost reduction for 16nm/10nm/7nm FPGA products

## UNMATCHED CUSTOMER VALUE

FPGA versatility addresses evolving needs of data era

IA+FPGA solutions creating unparalleled customer value

Expanded TAM and end-to-end lifecycle solutions with eASIC acquisition

## DISCLOSURES

Statements in this presentation that refer to business outlook, future plans and expectations are forward-looking statements that involve a number of risks and uncertainties. Words such as "anticipates," "expects," "intends," "goals," "plans," "believes," "seeks," "estimates," "continues," "may," "will," "would," "should," "could," and variations of such words and similar expressions are intended to identify such forward-looking statements. Statements that refer to or are based on projections, uncertain events or assumptions also identify forward-looking statements. Such statements are based on management's current expectations, unless an earlier date is indicated, and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in these forward-looking statements. Important factors that could cause actual results to differ materially from the company's expectations are set forth in Intel's earnings release dated July 26, 2018, which is included as an exhibit to Intel's Form 8-K furnished to the SEC on such date. Additional information regarding these and other factors that could affect Intel's results is included in Intel's SEC filings, including the company's most recent reports on Forms 10-K and 10-Q. Copies of Intel's Form 10-K, 10-Q and 8-K reports may be obtained by visiting our Investor Relations website at www.intc.com or the SEC's website at www.sec.gov.

All information in this presentation reflects management's views as of the date of this presentation, unless an earlier date is indicated. Intel does not undertake, and expressly disclaims any duty, to update any statement made in this presentation, whether as a result of new information, new developments or otherwise, except to the extent that disclosure may be required by law.